Changes to sequencer

Memory

The original sequencer uses 74LS189 as the memory chip. It is a 4*16 bit memory which dictates that the sequencer has 4 channels. Since I need 7 channels, something must be done. An easy way would be to use two 74LS189s in parallel. But I would like to have a non-volatile pattern memory, and also space for more than one patterns. Then the LS189 starts to be problematic.

Actually the whole idea about a non-volatile pattern memory occurred to me when I found couple of Mostek MK48Z02 ZeroPower RAM ICs from my junk collection. It is a static RAM with integrated lithium battery, made in the 80’s. It acts otherwise as a normal static RAM chip but if you cut the power, it will retain its contents using the integrated battery. Although manufacturer promises 10 years lifetime for the battery, it seems to work well now after almost 40 years!

The main downside of this IC is that it is intended to be connected to a microprocessor bus, meaning its interface is very different from 74LS189’s. The 74LS189 has separate data inputs and outputs, while MK48Z02 has a bi-directional data bus. It will need some extra logic to work in this circuit.

There

are three use

cases needed from RAM in this design: normal

data read, inverting a single bit (when pressing a sequencer button)

and clearing all (when pressing “clear pattern”). Because we

cannot write single bits, the whole word must always be written, the

single bit inversion is done by writing the RAM contents back and

selectively inverting or not inverting each bit. This is how the original design works, no new inventions here.

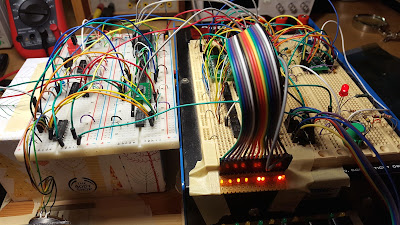

After

some testing with the breadboard, I came up with this kind of

circuit. Only one data bit is shown; in practice 7 data bits will be

used. Each data bit corresponds to one sequencer channel. 74HC563 is an octal D-latch with tri-state outputs, only one latch shown here.

The use cases are:

- Normally, when MEMW and CLR signals are inactive (high) the HC563 output is in high-impedance state, RAM WE is inactive and RAM OE is active. RAM data bus buffers are active and RAM contents are seen continuously at Dout.

- When MEMW goes low for a short time, an inverted or non-inverted copy of RAM data is latched to HC563 and written back to RAM. Signal INV determines whether the written bit is inverted or non-inverted.

- When CLR goes low, both HC563 and RAM stop driving the data bus and resistor pulls it to low state. This low state is written to RAM, effectively clearing it.

Finally, changing the RAM type did not require as many changes as I first thought. The 74HC563 was the only major addition here.

Now that I have plenty of RAM, I could store several patterns (in fact 128) just by setting the RAM upper address bits. But the selection switch for those would be enormous. So I think I will waste most of the RAM and use only two patterns, which can be selected with a simple two position switch.

Channel count

The original sequencer has only 4 channels, I need 7. Most of this was already solved by using an 8-bit wide RAM. But there are other issues also.

In the original design, the binary representation of the 2-bit channel number (0...3) is produced directly by a 2P4T rotary switch. With 7 channels, the channel number is 0...6 and needs 3 bits. With a similar solution, it would need a 3P7T switch, which are not easily available.

I solved this by using a normal 1P7T rotary switch, which are easy to get, and added a 74HC148 priority encoder, which produces the binary channel number. Because the channel number is always needed also in one-hot style (for the RAM bit inversion signals) this is now available directly from the switch output, and half of the original demux (U13) can be dropped. The other half is still needed, but now it is an 1:8 demux.

In some places the chip count has increased, because when using 4 channels, one 4-bit wide IC is enough, but 7 channels require two ICs. But the principle has not changed in those.

Trigger pulse length

The trigger pulses are very short in the original version, about 200 ns (signal STEP2 in the original schematic). My sound generators require 10 ms pulses, so this must be handled somehow.

The STEP2 signal, which determines the trigger pulse length, is produced by a monostable U8 in original schematic. The first thought is just to lengthen the monostable pulse to 10 ms. But it is not that simple: the button led multiplexing is going on all the time at about 1 kHz rate. During 10 ms the multiplexing circuitry has read the RAM several times at different addresses and data at the RAM output has changed many times.

This can be handled by adding latches and latch the trigger data from the data bus at the right moment. After 10 ms, the latches are cleared and the trigger pulses end. I added two 4-bit D-flip-flops (74HC175) and used about the original double monostable arrangement to generate the latch strobe and clear pulses. And now the original idea about lengthening the monotable pulse to 10 ms can actually be used. In the modified schematic, the monostable is IC2 and the control signals are TRIGSTB and TRIGCLR. Pulses look like this (the blue trace is TRIGSTB and the yellow trace is TRIGCLR):

Driving the button leds

I found from eBay some neat buttons which I plan to use as the sequencer step buttons, but they are designed to be driven directly with 6 V. They contain a led and a resistor. Because the leds are driven by multiplexing with 1:16 ratio, they should get more current than nominally. The resistor inside the button is very tricky to change and it should be done for all 16 buttons, so it is easier to give them more voltage.

Led takes about 4 mA current at 6 V. If we want to retain the brightness with 1:16 multiplexing, the current pulse should be 64 mA, which would need something over 50 volts. Quite an inconvenient voltage to use. Luckily, the leds are quite bright, even too bright for this use with the nominal current, so we can drop the current requirement. After some testing, the brightness seems convenient when driven with 15 V, which gives about 15 mA of current.

15 volts means we have to use separate driver ICs. I used the good old ULN2003 here. Three of them will be needed because there are 17 leds to drive. The 17th is the start/stop-button, it also has its own led. I also changed the original 1:16 demux 74154 to 4067, because ULN2003 needs active high drive.

External sync

Need of an external sync connector came to me as an afterthought and I did not test it on breadboard. This is always a big mistake: everything must be tested on breadboard before designing the PCB. As a consequence it does not work properly: when external clock pulses are coming from the connector and you try to stop the sequencer with the run/stop button, the step counter stops advancing, but there is nothing which would stop the pulses. So it keeps playing the first step continuously. I did not correct this, it would need some extra logic chips. So this feature is not very useful as it is now.

Other changes

Otherwise there are not many changes done to the original schematic. Just minor things like using monostable 4538 instead of 74HC123, because the former happened to be more easily available, and something like that. Most of the basic ideas have been retained.

I especially like how the stepping of the light in the buttons has been handled when the sequencer is running. If the status light in the button is off, the step light is shown during the first half of the step clock. But if the status light is on, the step light is on during the second half. This effect is very nice and clear to watch, and the circuitry used for implementing it is just brilliant. I would not have discovered that.

In the next post it is again printed circuit board design time, now for the sequencer boards.

Comments

Post a Comment